ARTIX-7 FPGA

לוח ליבה

AC7A200

מערכת על מודול

מדריך למשתמש

שיא גרסה

| גִרְסָה | תַאֲרִיך | שחרר לפי | תֵאוּר |

| גרסה 1.0 | 28-06-20 | רייצ'ל ג'ואו | שחרור ראשון |

חלק 1: מבוא לוח הליבה AC7A200

AC7A200 (דגם לוח ליבה, אותו הדבר למטה) לוח ליבה FPGA, הוא מבוסס על סדרת ARTIX-7 של XILINX 100T XC7A200T-2FBG484I. זהו לוח ליבה בעל ביצועים גבוהים עם מהירות גבוהה, רוחב פס גבוה וקיבולת גבוהה. זה מתאים לתקשורת נתונים במהירות גבוהה, עיבוד תמונת וידאו, רכישת נתונים במהירות גבוהה וכו '.

לוח הליבה AC7A200 זה משתמש בשני חלקים של שבב MT41J256M16HA-125 DDR3 של MICRON, לכל DDR קיבולת של 4Gbit; שני שבבי DDR משולבים לרוחב אפיק נתונים של 32 סיביות, ורוחב הפס של קריאה/כתיבה בין FPGA ל-DDR3 הוא עד 25Gb; תצורה כזו יכולה לענות על הצרכים של עיבוד נתונים ברוחב פס גבוה.

לוח הליבה AC7A200 מרחיב 180 יציאות IO סטנדרטיות ברמת 3.3V, 15 יציאות IO סטנדרטיות ברמת 1.5V ו-4 זוגות של אותות דיפרנציאליים RX/TX במהירות גבוהה GTP. עבור משתמשים שזקוקים להרבה IO, לוח הליבה הזה יהיה בחירה טובה. יתרה מכך, הניתוב בין שבב FPGA לממשק שווה באורך ועיבוד דיפרנציאלי, וגודל לוח הליבה הוא רק 2.36 אינץ' *2.36 אינץ', שמתאים מאוד לפיתוח משני.

איור 1-1: לוח הליבה AC7A200 (חזית View)

איור 1-2: לוח הליבה AC7A200 (אחורי View)

חלק 2: שבב FPGA

כפי שהוזכר לעיל, דגם ה-FPGA בו אנו משתמשים הוא XC7A200T-2FBG484I, השייך לסדרת ה-Artix-7 של Xilinx. דרגת המהירות היא 2, ודרגת הטמפרטורה היא דרגת תעשייה. דגם זה הוא חבילת FGG484 עם 484 פינים. כללי מתן שמות לשבב Xilinx ARTIX-7 FPGA כמפורט להלן

איור 2-1: הגדרת דגם השבב הספציפי של סדרת ARTIX-7

איור 2-2: שבב FPGA על הלוח

הפרמטרים העיקריים של שבב FPGA XC7A200T הם כדלקמן

| שֵׁם | פרמטרים ספציפיים |

| תאים לוגיים | 215360 |

| פרוסות | 16-02-92 |

| כפכפי CLB | 269200 |

| חסום זיכרון RAM(kb) | 13140 |

| פרוסות DSP | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| משדר GTP | 4 GTP, מקסימום 6.6Gb/s |

| ציון מהירות | -2 |

| דרגת טמפרטורה | תַעֲשִׂיָתִי |

מערכת אספקת חשמל FPGA

ספקי כוח Artix-7 FPGA הם VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC ו-VMGTAVTT. VCCINT הוא פין אספקת הליבה של FPGA, אשר צריך להיות מחובר ל-1.0V; VCCBRAM הוא פין אספקת הכוח של זיכרון RAM בלוק FPGA, מתחבר ל-1.0V; VCCAUX הוא פין ספק כוח עזר FPGA, חבר 1.8V; VCCO הוא הכרךtage של כל BANK של FPGA, כולל BANK0, BANK13~16, BANK34~35. בלוח הליבה AC7A200 FPGA, BANK34 ו-BANK35 צריכים להיות מחוברים ל-DDR3, הכרךtagהחיבור של BANK הוא 1.5V, והנפחtage של BANK אחר הוא 3.3V. ה-VCCO של BANK15 ו-BANK16 מופעל על ידי ה-LDO, וניתן לשנותו על ידי החלפת שבב LDO. VMGTAVCC הוא כרך האספקהtage של מקלט המשדר GTP הפנימי FPGA, מחובר ל-1.0V; VMGTAVTT הוא כרך הסיוםtage של מקלט המשדר GTP, מחובר ל-1.2V.

מערכת Artix-7 FPGA דורשת שרצף ההדלקה יהיה באמצעות VCCINT, לאחר מכן VCCBRAM, לאחר מכן VCCAUX, ולבסוף VCCO. אם ל-VCCINT ול-VCCBRAM יש אותו כרךtagה, ניתן להפעיל אותם בו-זמנית. סדר הכוח outages הוא הפוך. רצף ההפעלה של מקלט ה-GTP הוא VCCINT, ואז VMGTAVCC, ואז VMGTAVTT. אם ל-VCCINT ול-VMGTAVCC יש אותו כרךtagה, ניתן להפעיל אותם בו-זמנית. רצף הכיבוי הוא בדיוק ההפך מרצף ההפעלה.

חלק 3: קריסטל דיפרנציאלי פעיל

לוח הליבה AC7A200 מצויד בשני גבישי דיפרנציאל אקטיביים של Sitime, האחד הוא 200MHz, הדגם הוא SiT9102-200.00MHz, השעון הראשי של המערכת עבור FPGA ומשמש ליצירת שעון בקרה DDR3; השני הוא 125MHz, הדגם הוא SiT9102 -125MHz, כניסת שעון ייחוס עבור מקלטי משדר GTP.

חלק 3.1: שעון דיפרנציאל פעיל 200Mhz

G1 באיור 3-1 הוא גביש דיפרנציאלי אקטיבי של 200M המספק את מקור השעון של מערכת לוח הפיתוח. פלט הקריסטל מחובר לפין השעון העולמי BANK34 MRCC (R4 ו-T4) של ה-FPGA. ניתן להשתמש בשעון דיפרנציאלי זה של 200Mhz כדי להניע את לוגיקה המשתמש ב-FPGA. משתמשים יכולים להגדיר את ה-PLLs וה-DCMs בתוך ה-FPGA כדי ליצור שעונים בתדרים שונים.

איור 3-1: 200Mhz Active Differential Crystal Schematic

איור 3-2: גביש דיפרנציאלי פעיל 200Mhz על לוח הליבה

הקצאת פיני שעון דיפרנציאלי 200Mhz

| שם אות | PIN של FPGA |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

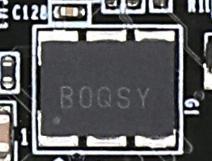

חלק 3.2: קריסטל דיפרנציאלי פעיל 125MHz

G2 באיור 3-3 הוא גביש הדיפרנציאלי הפעיל של 125MHz, שהוא שעון הכניסה הייחוס המסופק למודול GTP בתוך ה-FPGA. פלט הקריסטל מחובר לפיני השעון GTP BANK216 MGTREFCLK0P (F6) ו-MGTREFCLK0N (E6) של ה-FPGA.

איור 3-3: 125MHz Active Differential Crystal Schematic

איור 3-4: גביש דיפרנציאלי פעיל 125MHz על לוח הליבה

הקצאת פיני שעון דיפרנציאלי 125MHz

| שם נטו | PIN של FPGA |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

חלק 4: DDR3 DRAM

לוח הליבה FPGA AC7A200 מצויד בשני שבבי Micron 4Gbit (512MB) DDR3 (8Gbit בסך הכל), הדגם הוא MT41J256M16HA-125 (תואם ל-MT41K256M16HA-125). ל-DDR3 SDRAM מהירות פעולה מקסימלית של 400MHz (קצב נתונים 800Mbps). מערכת הזיכרון DDR3 מחוברת ישירות לממשק הזיכרון של BANK 34 ו-BANK35 של ה-FPGA. התצורה הספציפית של DDR3 SDRAM מוצגת בטבלה 4-1.

| מספר סיביות | דגם צ'יפ | יְכוֹלֶת | מִפְעָל |

| U5,U6 | MT41J256M16HA-125 | 256M x 16bit | מיקרון |

טבלה 4-1: תצורת DDR3 SDRAM

עיצוב החומרה של DDR3 דורש התייחסות קפדנית של שלמות האות. שקלנו באופן מלא את ההתנגדות התואמת לנגד/טרמינל, בקרת עכבת עקבות ובקרת אורך עקבות בתכנון המעגל ובתכנון ה-PCB כדי להבטיח פעולה מהירה ויציבה של DDR3. איור 4-1 מפרט את חיבור החומרה של DDR3 DRAM

איור 4-1: סכמטי DDR3 DRAM

איור 4-2: ה-DDR3 על לוח הליבה

הקצאת פינים DDR3 DRAM:

| שם נטו | שם PIN של FPGA | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

חלק 5: פלאש QSPI

לוח הליבה FPGA AC7A200 מצויד ב-128Mbit QSPI FLASH אחד, והדגם הוא N25Q128, המשתמש ב-3.3V CMOS voltagהתקן. בשל האופי הלא נדיף של QSPI FLASH, ניתן להשתמש בו כהתקן אתחול למערכת לאחסון תמונת האתחול של המערכת. תמונות אלו כוללות בעיקר סיביות FPGA files, קוד יישום ARM, קוד יישום הליבה הרכה ונתוני משתמש אחרים fileס. הדגמים הספציפיים והפרמטרים הקשורים של SPI FLASH מוצגים בטבלה 5-1.

| מַצָב | דֶגֶם | יְכוֹלֶת | מִפְעָל |

| U8 | N25Q128 | 128M Bit | נומוניקס |

טבלה 5-1: מפרט QSPI FLASH

QSPI FLASH מחובר לפינים הייעודיים של BANK0 ו-BANK14 של שבב FPGA. פין השעון מחובר ל-CCLK0 של BANK0, ואותות אחרים לבחירת נתונים ושבבים מחוברים לפיני D00~D03 ו-FCS של BANK14 בהתאמה. איור 5-1 מציג את חיבור החומרה של QSPI Flash.

איור 5-1: QSPI Flash Schematic

הקצאות סיכות פלאש QSPI:

| שם נטו | שם PIN של FPGA | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

איור 5-2: QSPI FLASH בלוח הליבה

חלק 6: נורת LED על לוח ליבה

ישנן 3 נורות LED אדומות על לוח הליבה AC7A200 FPGA, אחת מהן היא נורית חיווי המתח (PWR), אחת היא נורית LED בתצורה (DONE), ואחת היא נורית LED למשתמש. כאשר לוח הליבה מופעל, מחוון המתח יידלק; כאשר ה-FPGA מוגדר, נורית התצורה תידלק. נורית ה-LED של המשתמש מחוברת ל-IO של BANK34, המשתמש יכול לשלוט בדלקה וכיבוי האור על ידי התוכנית. כאשר ה-IO כרךtagהמחובר ל-LED של המשתמש גבוה, נורית המשתמש דולקת. כאשר החיבור IO כרךtage נמוך, נורית המשתמש תכבה. התרשים הסכמטי של חיבור החומרה של אור LED מוצג באיור 6-1:

איור 6-1: נורות LED על לוח הליבה

איור 6-2: נורות LED על לוח הליבה

הקצאת פינים של נוריות משתמש

| שם אות | שם Pin FPGA | מספר PIN של FPGA | תֵאוּר |

| LED1 | IO_L15N_T2_DQS_34 | W5 | משתמש LED |

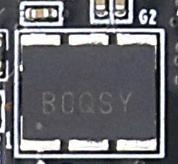

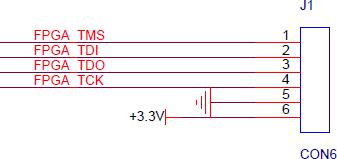

חלק 7: יTAG מִמְשָׁק

ה- J.TAG שקע הבדיקה J1 שמור בלוח הליבה של AC7A200 עבור JTAG הורדה וניפוי באגים כאשר לוח הליבה משמש לבד. איור 7-1 הוא החלק הסכמטי של ה-JTAG נמל, הכולל TMS, TDI, TDO, TCK. , GND, +3.3V ששת האותות האלה.

איור 7-1: JTAG סכמטי ממשק

ה- J.TAG ממשק J1 בלוח הליבה AC7A200 FPGA משתמש בחור בדיקה בעל 6 פינים בגובה 2.54 מ"מ בשורה אחת. אם אתה צריך להשתמש ב-JTAG מחבר לניפוי באגים בלוח הליבה, עליך להלחים כותרת פינים בעלת 6 פינים בשורה אחת.

איור 7-2 מציג את ה-JTAG ממשק J1 בלוח הליבה AC7A200 FPGA.

איור 7-2 JTAG ממשק על לוח ליבה

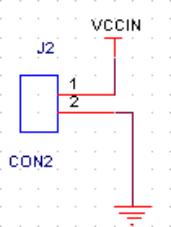

חלק 8: ממשק כוח על לוח הליבה

על מנת לגרום ללוח הליבה AC7A200 FPGA לעבוד לבד, לוח הליבה שמור ממשק אספקת חשמל בעל 2 פינים J2. אם המשתמש רוצה לנפות באגים בנפרד בתפקוד לוח הליבה (ללא לוח הספק), ההתקן החיצוני צריך לספק +5V כדי לספק חשמל ללוח הליבה.

איור 8-1: סכימה של ממשק כוח על לוח הליבה

איור 8-2: ממשק חשמל בלוח הליבה

חלק 9: הקצאת פינים של מחברי לוח ללוח

ללוח הליבה יש בסך הכל ארבעה מחברי לוח ללוח מהירים.

לוח הליבה משתמש בארבעה מחברים בין-לוחים בעלי 80 פינים כדי להתחבר ללוח המוביל. יציאת ה-IO של ה-FPGA מחוברת לארבעת המחברים על ידי ניתוב דיפרנציאלי. מרווח הפינים של המחברים הוא 0.5 מ"מ, הכנס ללוח ללוח מחברים בלוח הספק לתקשורת נתונים במהירות גבוהה.

מחברי לוח ללוח CON1

מחברי הלוח ללוח עם 80 פינים CON1, המשמשים לחיבור עם ספק הכוח VCCIN (+5V) והארקה בלוח הספק, מרחיבים את ה-IOs הרגילים של ה-FPGA. יש לציין כאן ש-15 פינים של CON1 מחוברים ליציאת IO של BANK34, מכיוון שחיבור BANK34 מחובר ל-DDR3. לכן, הכרךtagהתקן של כל ה-IO של BANK34 זה הוא 1.5V.

הקצאת פינים של מחברי לוח ללוח CON1

| CON1 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

CON1 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

| PIN1 | VCCIN | – | +5V | PIN2 | VCCIN | – | +5V |

| PIN3 | VCCIN | – | +5V | PIN4 | VCCIN | – | +5V |

| PIN5 | VCCIN | – | +5V | PIN6 | VCCIN | – | +5V |

| PIN7 | VCCIN | – | +5V | PIN8 | VCCIN | – | +5V |

| PIN9 | GND | – | טָחוּן | PIN10 | GND | – | טָחוּן |

| PIN11 | NC | – | NC | PIN12 | NC | – | NC |

| PIN13 | NC | – | NC | PIN14 | NC | – | NC |

| PIN15 | NC | – | NC | PIN16 | B13_L4_P | AA15 | 3.3V |

| PIN17 | NC | – | NC | PIN18 | B13_L4_N | AB15 | 3.3V |

| PIN19 | GND | – | טָחוּן | PIN20 | GND | – | טָחוּן |

| PIN21 | B13_L5_P | Y13 | 3.3V | PIN22 | B13_L1_P | Y16 | 3.3V |

| PIN23 | B13_L5_N | AA14 | 3.3V | PIN24 | B13_L1_N | AA16 | 3.3V |

| PIN25 | B13_L7_P | AB11 | 3.3V | PIN26 | B13_L2_P | AB16 | 3.3V |

| PIN27 | B13_L7_P | AB12 | 3.3V | PIN28 | B13_L2_N | AB17 | 3.3V |

| PIN29 | GND | – | טָחוּן | PIN30 | GND | – | טָחוּן |

| PIN31 | B13_L3_P | AA13 | 3.3V | PIN32 | B13_L6_P | W14 | 3.3V |

| PIN33 | B13_L3_N | AB13 | 3.3V | PIN34 | B13_L6_N | Y14 | 3.3V |

| PIN35 | B34_L23_P | Y8 | 1.5V | PIN36 | B34_L20_P | AB7 | 1.5V |

| PIN37 | B34_L23_N | Y7 | 1.5V | PIN38 | B34_L20_N | AB6 | 1.5V |

| PIN39 | GND | – | טָחוּן | PIN40 | GND | – | טָחוּן |

| PIN41 | B34_L18_N | AA6 | 1.5V | PIN42 | B34_L21_N | V8 | 1.5V |

| PIN43 | B34_L18_P | Y6 | 1.5V | PIN44 | B34_L21_P | V9 | 1.5V |

| PIN45 | B34_L19_P | V7 | 1.5V | PIN46 | B34_L22_P | AA8 | 1.5V |

| PIN47 | B34_L19_N | W7 | 1.5V | PIN48 | B34_L22_N | AB8 | 1.5V |

| PIN49 | GND | – | טָחוּן | PIN50 | GND | – | טָחוּן |

| PIN51 | XADC_VN | M9 | אנלוגי | PIN52 | NC | ||

| PIN53 | XADC_VP | L10 | אנלוגי | PIN54 | B34_L25 | U7 | 1.5V |

| PIN55 | NC | – | NC | PIN56 | B34_L24_P | W9 | 1.5V |

| PIN57 | NC | – | NC | PIN58 | B34_L24_N | Y9 | 1.5V |

| PIN59 | GND | – | טָחוּן | PIN60 | GND | – | טָחוּן |

| PIN61 | B16_L1_N | F14 | 3.3V | PIN62 | NC | – | NC |

| PIN63 | B16_L1_P | F13 | 3.3V | PIN64 | NC | – | NC |

| PIN65 | B16_L4_N | E14 | 3.3V | PIN66 | NC | – | NC |

| PIN67 | B16_L4_P | E13 | 3.3V | PIN68 | NC | – | NC |

| PIN69 | GND | – | טָחוּן | PIN70 | GND | – | טָחוּן |

| PIN71 | B16_L6_N | D15 | 3.3V | PIN72 | NC | – | NC |

| PIN73 | B16_L6_P | D14 | 3.3V | PIN74 | NC | – | NC |

| PIN75 | B16_L8_P | C13 | 3.3V | PIN76 | NC | – | NC |

| PIN77 | B16_L8_N | B13 | 3.3V | PIN78 | NC | – | NC |

| PIN79 | NC | – | NC | PIN80 | NC | – | NC |

איור 9-1: מחברי לוח ללוח CON1 בלוח הליבה

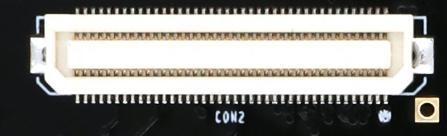

מחברי לוח ללוח CON2

כותרת החיבור הנשית 80 פינים CON2 משמשת להרחבת ה-IO הרגיל של BANK13 ו-BANK14 של FPGA. הכרךtagהסטנדרטים של שני הבנקים הם 3.3V.

הקצאת פינים של מחברי לוח ללוח CON2

| CON2 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

CON2 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

| PIN1 | B13_L16_P | W15 | 3.3V | PIN2 | B14_L16_P | V17 | 3.3V |

| PIN3 | B13_L16_N | W16 | 3.3V | PIN4 | B14_L16_N | W17 | 3.3V |

| PIN5 | B13_L15_P | T14 | 3.3V | PIN6 | B13_L14_P | U15 | 3.3V |

| PIN7 | B13_L15_N | T15 | 3.3V | PIN8 | B13_L14_N | V15 | 3.3V |

| PIN9 | GND | – | טָחוּן | PIN10 | GND | – | טָחוּן |

| PIN11 | B13_L13_P | V13 | 3.3V | PIN12 | B14_L10_P | AB21 | 3.3V |

| PIN13 | B13_L13_N | V14 | 3.3V | PIN14 | B14_L10_N | AB22 | 3.3V |

| PIN15 | B13_L12_P | W11 | 3.3V | PIN16 | B14_L8_N | AA21 | 3.3V |

| PIN17 | B13_L12_N | W12 | 3.3V | PIN18 | B14_L8_P | AA20 | 3.3V |

| PIN19 | GND | – | טָחוּן | PIN20 | GND | – | טָחוּן |

| PIN21 | B13_L11_P | Y11 | 3.3V | PIN22 | B14_L15_N | AB20 | 3.3V |

| PIN23 | B13_L11_N | Y12 | 3.3V | PIN24 | B14_L15_P | AA19 | 3.3V |

| PIN25 | B13_L10_P | V10 | 3.3V | PIN26 | B14_L17_P | AA18 | 3.3V |

| PIN27 | B13_L10_N | W10 | 3.3V | PIN28 | B14_L17_N | AB18 | 3.3V |

| PIN29 | GND | – | טָחוּן | PIN30 | GND | – | טָחוּן |

| PIN31 | B13_L9_N | AA11 | 3.3V | PIN32 | B14_L6_N | T20 | 3.3V |

| PIN33 | B13_L9_P | AA10 | 3.3V | PIN34 | B13_IO0 | Y17 | 3.3V |

| PIN35 | B13_L8_N | AB10 | 3.3V | PIN36 | B14_L7_N | W22 | 3.3V |

| PIN37 | B13_L8_P | AA9 | 3.3V | PIN38 | B14_L7_P | W21 | 3.3V |

| PIN39 | GND | – | טָחוּן | PIN40 | GND | – | טָחוּן |

| PIN41 | B14_L11_N | V20 | 3.3V | PIN42 | B14_L4_P | T21 | 3.3V |

| PIN43 | B14_L11_P | U20 | 3.3V | PIN44 | B14_L4_N | U21 | 3.3V |

| PIN45 | B14_L14_N | V19 | 3.3V | PIN46 | B14_L9_P | Y21 | 3.3V |

| PIN47 | B14_L14_P | V18 | 3.3V | PIN48 | B14_L9_N | Y22 | 3.3V |

| PIN49 | GND | – | טָחוּן | PIN50 | GND | – | טָחוּן |

| PIN51 | B14_L5_N | R19 | 3.3V | PIN52 | B14_L12_N | W20 | 3.3V |

| PIN53 | B14_L5_P | P19 | 3.3V | PIN54 | B14_L12_P | W19 | 3.3V |

| PIN55 | B14_L18_N | U18 | 3.3V | PIN56 | B14_L13_N | Y19 | 3.3V |

| PIN57 | B14_L18_P | U17 | 3.3V | PIN58 | B14_L13_P | Y18 | 3.3V |

| PIN59 | GND | – | טָחוּן | PIN60 | GND | – | טָחוּן |

| PIN61 | B13_L17_P | T16 | 3.3V | PIN62 | B14_L3_N | V22 | 3.3V |

| PIN63 | B13_L17_N | U16 | 3.3V | PIN64 | B14_L3_P | U22 | 3.3V |

| PIN65 | B14_L21_N | P17 | 3.3V | PIN66 | B14_L20_N | T18 | 3.3V |

| PIN67 | B14_L21_P | N17 | 3.3V | PIN68 | B14_L20_P | R18 | 3.3V |

| PIN69 | GND | – | טָחוּן | PIN70 | GND | – | טָחוּן |

| PIN71 | B14_L22_P | P15 | 3.3V | PIN72 | B14_L19_N | R14 | 3.3V |

| PIN73 | B14_L22_N | R16 | 3.3V | PIN74 | B14_L19_P | P14 | 3.3V |

| PIN75 | B14_L24_N | R17 | 3.3V | PIN76 | B14_L23_P | N13 | 3.3V |

| PIN77 | B14_L24_P | P16 | 3.3V | PIN78 | B14_L23_N | N14 | 3.3V |

| PIN79 | B14_IO0 | P20 | 3.3V | PIN80 | B14_IO25 | N15 | 3.3V |

איור 9-2: מחברי לוח ללוח CON2 בלוח הליבה

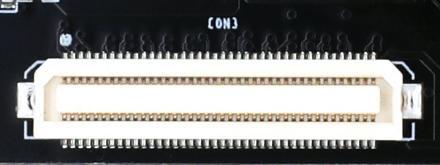

מחברי לוח ללוח CON3

מחבר 80 פינים CON3 משמש להרחבת ה-IO הרגיל של BANK15 ו-BANK16 של FPGA. בנוסף, ארבעה JTAG אותות מחוברים גם ללוח הספק דרך מחבר CON3. הכרךtagהסטנדרטים של BANK15 ו-BANK16 ניתנים להתאמה באמצעות שבב LDO. ברירת המחדל של LDO המותקנת היא 3.3V. אם אתה רוצה להוציא רמות סטנדרטיות אחרות, אתה יכול להחליף אותו ב-LDO מתאים.

הקצאת פינים של מחברי לוח ללוח CON3

| CON3 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

CON3 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

| PIN1 | B15_IO0 | J16 | 3.3V | PIN2 | B15_IO25 | M17 | 3.3V |

| PIN3 | B16_IO0 | F15 | 3.3V | PIN4 | B16_IO25 | F21 | 3.3V |

| PIN5 | B15_L4_P | G17 | 3.3V | PIN6 | B16_L21_N | A21 | 3.3V |

| PIN7 | B15_L4_N | G18 | 3.3V | PIN8 | B16_L21_P | B21 | 3.3V |

| PIN9 | GND | – | טָחוּן | PIN10 | GND | – | טָחוּן |

| PIN11 | B15_L2_P | G15 | 3.3V | PIN12 | B16_L23_P | E21 | 3.3V |

| PIN13 | B15_L2_N | G16 | 3.3V | PIN14 | B16_L23_N | D21 | 3.3V |

| PIN15 | B15_L12_P | J19 | 3.3V | PIN16 | B16_L22_P | E22 | 3.3V |

| PIN17 | B15_L12_N | H19 | 3.3V | PIN18 | B16_L22_N | D22 | 3.3V |

| PIN19 | GND | – | טָחוּן | PIN20 | GND | – | טָחוּן |

| PIN21 | B15_L11_P | J20 | 3.3V | PIN22 | B16_L24_P | G21 | 3.3V |

| PIN23 | B15_L11_N | J21 | 3.3V | PIN24 | B16_L24_N | G22 | 3.3V |

| PIN25 | B15_L1_N | G13 | 3.3V | PIN26 | B15_L8_N | G20 | 3.3V |

| PIN27 | B15_L1_P | H13 | 3.3V | PIN28 | B15_L8_P | H20 | 3.3V |

| PIN29 | GND | – | טָחוּן | PIN30 | GND | – | טָחוּן |

| PIN31 | B15_L5_P | J15 | 3.3V | PIN32 | B15_L7_N | H22 | 3.3V |

| PIN33 | B15_L5_N | H15 | 3.3V | PIN34 | B15_L7_P | J22 | 3.3V |

| PIN35 | B15_L3_N | H14 | 3.3V | PIN36 | B15_L9_P | K21 | 3.3V |

| PIN37 | B15_L3_P | J14 | 3.3V | PIN38 | B15_L9_N | K22 | 3.3V |

| PIN39 | GND | – | טָחוּן | PIN40 | GND | – | טָחוּן |

| PIN41 | B15_L19_P | K13 | 3.3V | PIN42 | B15_L15_N | M22 | 3.3V |

| PIN43 | B15_L19_N | K14 | 3.3V | PIN44 | B15_L15_P | N22 | 3.3V |

| PIN45 | B15_L20_P | M13 | 3.3V | PIN46 | B15_L6_N | H18 | 3.3V |

| PIN47 | B15_L20_N | L13 | 3.3V | PIN48 | B15_L6_P | H17 | 3.3V |

| PIN49 | GND | – | טָחוּן | PIN50 | GND | – | טָחוּן |

| PIN51 | B15_L14_P | L19 | 3.3V | PIN52 | B15_L13_N | K19 | 3.3V |

| PIN53 | B15_L14_N | L20 | 3.3V | PIN54 | B15_L13_P | K18 | 3.3V |

| PIN55 | B15_L21_P | K17 | 3.3V | PIN56 | B15_L10_P | M21 | 3.3V |

| PIN57 | B15_L21_N | J17 | 3.3V | PIN58 | B15_L10_N | L21 | 3.3V |

| PIN59 | GND | – | טָחוּן | PIN60 | GND | – | טָחוּן |

| PIN61 | B15_L23_P | L16 | 3.3V | PIN62 | B15_L18_P | N20 | 3.3V |

| PIN63 | B15_L23_N | K16 | 3.3V | PIN64 | B15_L18_N | M20 | 3.3V |

| PIN65 | B15_L22_P | L14 | 3.3V | PIN66 | B15_L17_N | N19 | 3.3V |

| PIN67 | B15_L22_N | L15 | 3.3V | PIN68 | B15_L17_P | N18 | 3.3V |

| PIN69 | GND | – | טָחוּן | PIN70 | GND | – | טָחוּן |

| PIN71 | B15_L24_P | M15 | 3.3V | PIN72 | B15_L16_P | M18 | 3.3V |

| PIN73 | B15_L24_N | M16 | 3.3V | PIN74 | B15_L16_N | L18 | 3.3V |

| PIN75 | NC | – | PIN76 | NC | – | ||

| PIN77 | FPGA_TCK | V12 | 3.3V | PIN78 | FPGA_TDI | R13 | 3.3V |

| PIN79 | FPGA_TDO | U13 | 3.3V | PIN80 | FPGA_TMS | T13 | 3.3V |

איור 9-3: מחברי לוח ללוח CON3 בלוח הליבה

מחברי לוח ללוח CON4

מחבר ה-80 פינים CON4 משמש להרחבת הנתונים והשעון הרגילים של IO ו-GTP במהירות גבוהה של FPGA BANK16. הכרךtagניתן לכוונן את התקן של יציאת ה-IO של BANK16 באמצעות שבב LDO. ברירת המחדל המותקנת של LDO היא 3.3V. אם המשתמש רוצה להוציא רמות סטנדרטיות אחרות, ניתן להחליפו ב-LDO מתאים. הנתונים המהירים ואותות השעון של ה-GTP מנותבים באופן דיפרנציאלי על לוח הליבה. קווי הנתונים שווים באורכם ונשמרים במרווח מסוים כדי למנוע הפרעות אות.

הקצאת פינים של מחברי לוח ללוח CON4

| CON4 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

CON4 פִּין |

נֶטוֹ שֵׁם |

FPGA פִּין |

כרך ידtage רָמָה |

| PIN1 | NC | – | – | PIN2 | – | – | |

| PIN3 | NC | – | – | PIN4 | – | – | |

| PIN5 | NC | – | – | PIN6 | – | – | |

| PIN7 | NC | – | – | PIN8 | – | – | |

| PIN9 | GND | – | טָחוּן | PIN10 | GND | – | טָחוּן |

| PIN11 | NC | – | – | PIN12 | MGT_TX2_P | B6 | הבדל |

| PIN13 | NC | – | – | PIN14 | MGT_TX2_N | A6 | הבדל |

| PIN15 | GND | – | טָחוּן | PIN16 | GND | – | טָחוּן |

| PIN17 | MGT_TX3_P | D7 | הבדל | PIN18 | MGT_RX2_P | B10 | הבדל |

| PIN19 | MGT_TX3_N | C7 | הבדל | PIN20 | MGT_RX2_N | A10 | הבדל |

| PIN21 | GND | – | טָחוּן | PIN22 | GND | – | טָחוּן |

| PIN23 | MGT_RX3_P | D9 | הבדל | PIN24 | MGT_TX0_P | B4 | הבדל |

| PIN25 | MGT_RX3_N | C9 | הבדל | PIN26 | MGT_TX0_N | A4 | הבדל |

| PIN27 | GND | – | טָחוּן | PIN28 | GND | – | טָחוּן |

| PIN29 | MGT_TX1_P | D5 | הבדל | PIN30 | MGT_RX0_P | B8 | הבדל |

| PIN31 | MGT_TX1_N | C5 | הבדל | PIN32 | MGT_RX0_N | A8 | הבדל |

| PIN33 | GND | – | טָחוּן | PIN34 | GND | – | טָחוּן |

| PIN35 | MGT_RX1_P | D11 | הבדל | PIN36 | MGT_CLK1_P | F10 | הבדל |

| PIN37 | MGT_RX1_N | C11 | הבדל | PIN38 | MGT_CLK1_N | E10 | הבדל |

| PIN39 | GND | – | טָחוּן | PIN40 | GND | – | טָחוּן |

| PIN41 | B16_L5_P | E16 | 3.3V | PIN42 | B16_L2_P | F16 | 3.3V |

| PIN43 | B16_L5_N | D16 | 3.3V | PIN44 | B16_L2_N | E17 | 3.3V |

| PIN45 | B16_L7_P | B15 | 3.3V | PIN46 | B16_L3_P | C14 | 3.3V |

| PIN47 | B16_L7_N | B16 | 3.3V | PIN48 | B16_L3_N | C15 | 3.3V |

| PIN49 | GND | – | טָחוּן | PIN50 | GND | – | טָחוּן |

| PIN51 | B16_L9_P | A15 | 3.3V | PIN52 | B16_L10_P | A13 | 3.3V |

| PIN53 | B16_L9_N | A16 | 3.3V | PIN54 | B16_L10_N | A14 | 3.3V |

| PIN55 | B16_L11_P | B17 | 3.3V | PIN56 | B16_L12_P | D17 | 3.3V |

| PIN57 | B16_L11_N | B18 | 3.3V | PIN58 | B16_L12_N | C17 | 3.3V |

| PIN59 | GND | – | טָחוּן | PIN60 | GND | – | טָחוּן |

| PIN61 | B16_L13_P | C18 | 3.3V | PIN62 | B16_L14_P | E19 | 3.3V |

| PIN63 | B16_L13_N | C19 | 3.3V | PIN64 | B16_L14_N | D19 | 3.3V |

| PIN65 | B16_L15_P | F18 | 3.3V | PIN66 | B16_L16_P | B20 | 3.3V |

| PIN67 | B16_L15_N | E18 | 3.3V | PIN68 | B16_L16_N | A20 | 3.3V |

| PIN69 | GND | – | טָחוּן | PIN70 | GND | – | טָחוּן |

| PIN71 | B16_L17_P | A18 | 3.3V | PIN72 | B16_L18_P | F19 | 3.3V |

| PIN73 | B16_L17_N | A19 | 3.3V | PIN74 | B16_L18_N | F20 | 3.3V |

| PIN75 | B16_L19_P | D20 | 3.3V | PIN76 | B16_L20_P | C22 | 3.3V |

| PIN77 | B16_L19_N | C20 | 3.3V | PIN78 | B16_L20_N | B22 | 3.3V |

| PIN79 | NC | – | PIN80 | NC | – |

איור 9-4: מחברי לוח ללוח CON4 בלוח הליבה

חלק 10: אספקת חשמל

לוח הליבה AC7A200 FPGA מופעל על ידי DC5V באמצעות לוח נשא, והוא מופעל על ידי ממשק Mini USB כאשר הוא משמש לבד. אנא היזהר לא לספק חשמל על ידי ה-Mini USB ולוח הספק בו-זמנית כדי למנוע נזק. דיאגרמת תכנון ספק הכוח על הלוח מוצגת באיור 10-1.

איור 10-1: סכימה של ספק כוח על לוח הליבה

לוח הליבה מופעל על ידי +5V ומומר ל-+3.3V, +1.5V, +1.8V, +1.0V אספקת כוח ארבע כיוונית באמצעות שלושה שבבי ספק כוח DC/DC TLV62130RGT. הזרם של +1.0V יכול להיות עד 6A, ושלושת זרמי המוצא האחרים יכולים להיות עד 3A. ה-VCCIO נוצר על ידי LDOSPX3819M5-3-3 אחד. VCCIO מספקת בעיקר חשמל ל-BANK15 ו-BANK16 של FPGA. משתמשים יכולים לשנות את ה-IO של BANK15,16 לנפח אחרtage סטנדרטים על ידי החלפת שבב LDO שלהם. ה-1.5V מייצר את כרך VTT ו-VREFtagזה נדרש על ידי DDR3 באמצעות TPS51200 של TI. ספק הכוח של 1.8V של MGTAVTT ו-MGTAVCC עבור מקלט המשדר GTP נוצר על ידי שבב TPS74801 של TI. הפונקציות של כל חלוקת כוח מוצגות בטבלה הבאה:

| ספק כוח | פוּנקצִיָה |

| +1.0V | FPGA Core Voltage |

| +1.8V | כרך עזר FPGAtagה, ספק כוח TPS74801 |

| +3.3V | VCCIO של Bank0,Bank13 ו-Bank14 של FPGA, QSIP FLASH, Clock Crystal |

| +1.5V | DDR3, Bank34 ו-Bank35 של FPGA |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA Bank15, Bank16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 של FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 של FPGA |

מכיוון שלספק הכוח של Artix-7 FPGA יש את דרישת רצף ההדלקה, בתכנון המעגל, תכננו בהתאם לדרישות ההספק של השבב, וההפעלה היא 1.0V->1.8V->(1.5 V, 3.3V, VCCIO) ו-1.0V-> MGTAVCC -> MGTAVTT, עיצוב המעגל כדי להבטיח את הפעולה הרגילה של השבב.

מעגל הכוח בלוח הליבה AC7A200 FPGA מוצג באיור 10-2:

איור 10-2: ספק כוח על לוח הליבה AC7A200 FPGA

חלק 11: מימד גודל

איור 11-1: לוח AC7A200 FPGA Core (למעלה View)

איור 11-2: לוח AC7A200 FPGA Core (למטה View)

מסמכים / משאבים

|

לוח פיתוח ALINX AC7A200 ARTIX-7 FPGA [pdfמדריך למשתמש AC7A200 ARTIX-7 FPGA Development Board, AC7A200, ARTIX-7 FPGA Development Board, FPGA Development Board, Board Development, Board |